TECHNOLOGY

Design Concept

IOCore® is an ultra-compact optical transceiver that integrates optical transmitter and receiver functions on a single chip. It is designed for short distance interconnections over multimode fiber.

It focuses on computing applications where low power consumption and low latency are important, and supports NRZ signal transmission from 1 Gbps to 25 Gbps and 32 Gbps without CDR.

It uses a Fabry-Perot-type quantum dot laser as the light source that can operate for long periods of time over an industrial temperature range with extremely high reliability.

It is an optical building block that can be flexibly combined with optical components such as front pluggable transceiver modules and co-packaged optical modules.

Si photonics

Structure

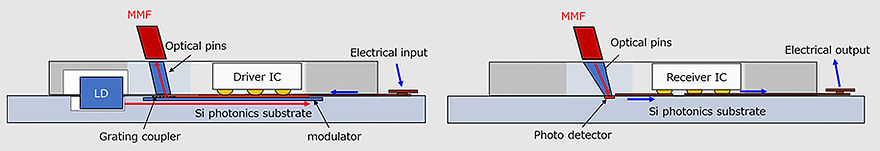

The Silicon Photonics Integrated Circuit in the IOCore® comprises Mach-Zehnder Interference (MZI) modulators, Germanium photodetectors, Spot Size Converters (SSC) for Laser Diode (LD) coupling and Vertical Grating Couplers.

The substrate includes a cavity and alignment markers allowing the source LD to be passively aligned and mounted into the chip.

Electrical contacts are provided on the optical integrated circuit including pads for flip-chip mounting the driver IC to the modulator, and electrical input/output terminals on the periphery.

The process uses a 300 mm SOI wafer.

300mm SOI Wafers

Ar immersion technology is applied to 300 mm SOI wafers. The device is designed with robustness in mind. Therefore, the characteristics in the wafer are very uniform and chips can be obtained with a very high yield.

By producing smaller chips in higher yields than anywhere else, we have succeeded in significantly reducing the cost of our Si photonic chips.

Quantum Dot LASER

Industrial Temperature

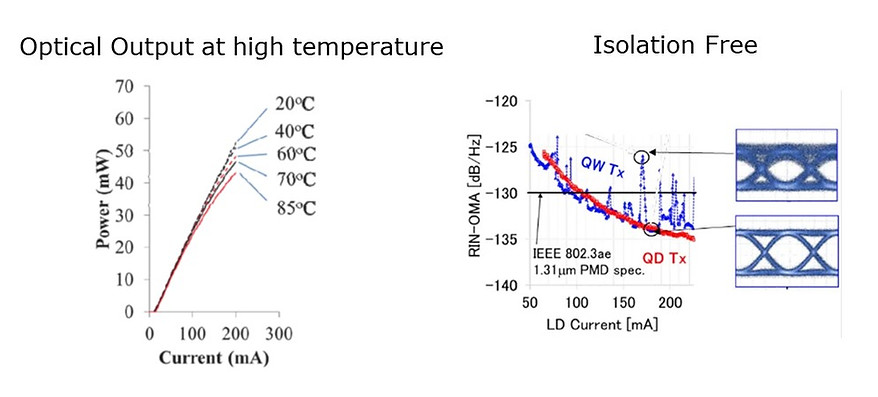

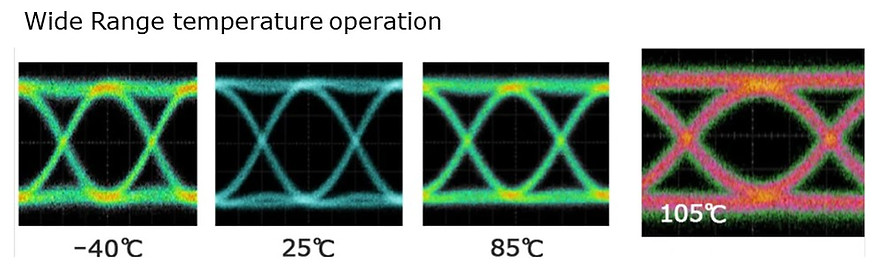

In the MZI modulator, the expression for modulation efficiency is given by C × V (where C =Capacitance, V = supply voltage). As C is temperature independent and the modulation voltage is constant, the frequency band is stable over a wide temperature range. Therefore, a very stable optical output waveform with low jitter can be obtained over a wide temperature range.

A Quantum Dot Fabry-Perot laser is used as the light source. Quantum Dot lasers exhibit low temperature dependence in their L-I characteristics and can provide sufficient optical output even at very high temperatures. Also, it includes the feature that reflected return light noise is very small. IOCore® can therefore be used over a wide temperature range. The light output waveform of the current product from -40 °C to 85 °C is shown.

When an IOCore® is mounted around a logic LSI (e.g. a Co-Packaged Optical module) or used in a harsh environment, operation at 100 °C or higher may be required. We are developing an IOCore® that operates at temperatures above 100 °C, and plan to release it in the near future.

The following images show an example of an optical output waveform at 100 °C.

Packaging

Overview

IOCore® consists of a Si photonic integrated circuit and substrate, on which ICs and LDs are mounted, and optical coupling structures called optical pins, which allow optical fibers to be connected to the chip robustly and with low loss. Optical pins are vertical optical waveguides made of resin and fabricated using photolithographic processes. The LD is positioned and mounted with high precision using passive alignment structures. Assembly is carried out by proprietary automated processes and equipment.

Optical fibers are not connected directly to the Si photonic substrate, but to the optical pins on a separate higher interface, which allows for a more robust and lower cost connection.

There is no need to secure an area for mounting optical fibers directly to the chip surface, thus contributing to the further miniaturization of Si photonic chips.

Optical Pins

One of the key features of the IOCore® is the optical pin structure, which couples light from the IOCore® transmitters to the multimode fiber (MMF) interface, and from the MMF interface to receivers in the IOCore®.

Variations in transmitter temperature give rise to shifts in the LD wavelength, which in turn cause changes in the angle of emission through the grating couplers. The optical pins on the transmitter side are designed to confine the light emitted from the grating couplers in their cores, even when the emission angle varies. This allows stable optical connections to be maintained even at temperatures exceeding 100 °C or higher.

The optical pins on the receiver side are tapered to efficiently capture the light from the larger multimode fiber core, and guide and compress it into the smaller active area of the photodetector.

The optical pins are largely temperature independent with a misalignment tolerance higher than ± 10 µm to mount the MMF array, which is over an order of magnitude higher than competing silicon photonics chips. The increased misalignment tolerance of the optical interface allows for a low-loss optical connection to be maintained over a longer time and under harsher conditions, thus substantially increasing the reliability of the critical optical connection.

LD Passive Alignment

The IOCore® batch assembly process divides the Si photonics wafer into 4 x 4 (total of 16 pcs) tiles with components assembled on a tile-by-tile basis. The LDs are mounted into their IOCore® tiles through an automated alignment process using passive alignment features patterned both on the Si photonic chip and the LD. Using conventional pick-and-place techniques and equipment, this gives rise to a positional accuracy of 0.5 µm or less.

The optical pins are formed photolithographically on the 16 IOCore® tiles using an automatic exposure machine with ordinary lenses, thus low cost and high productivity can be achieved.

Finally we are developing an automated assembly machine, that can mount optical fibers passively onto the IOCore®. Passive automated alignment is made possible by the increased misalignment tolerance afforded by the optical pins and the MMFs. Further cost reduction is thus achieved, compared to competing single mode devices in the market, by using lower cost, lower precision MMF components instead of higher precision single mode fibers (SMF) and associated components.

If you would like to build a custom module, we can help you take advantage of this passive optical connector.

Immersion Cooling

Heat management is one of the biggest issue in advanced computing. Immersion cooling is expected to be the solution for heat management to enhance the performance.

IOCore® micro transceiver package is designed not only for easy assembly but for robustness in harsh environment applications.

In immersive environments, our optical design having no air gap in optical path makes IOCore® unaffected by coolant liquid.

IOCore® demonstrated stable operation in immersive environments with mainstream immersion coolants of both single phase and two phase. Also, long-term reliability in immersive environments including influences of coolant liquids to optical components has been examined.

Detailed results, evaluation kit for immersive circumstances are available. Please request HERE.

Roadmap